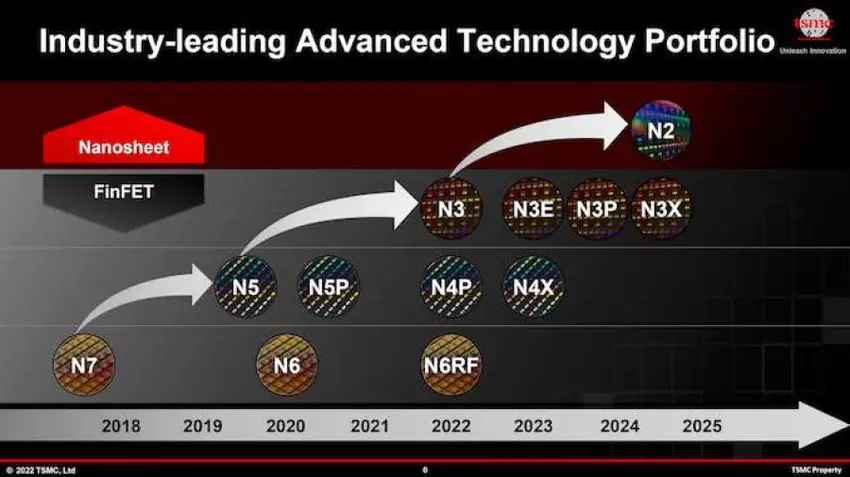

TSMC planuje uruchomić 3 nm w 2023 r., a 2 nm w 2025 r.

Podczas sympozjum technologicznego TSMC w 2022 r. TSMC nakreśliło harmonogram rozwoju swoich chipów. W drugiej połowie tego roku TSMC po raz pierwszy na świecie wypuści chipy 3 nm, a technologia 2 nm zadebiutuje w 2025 roku. Będzie pięć poziomów chipów 3 nm: N3 (ulepszony), N3E (ulepszony), N3P (Zwiększona wydajność), N3S (Zwiększona gęstość) i N3X (Ultra wysoka wydajność).

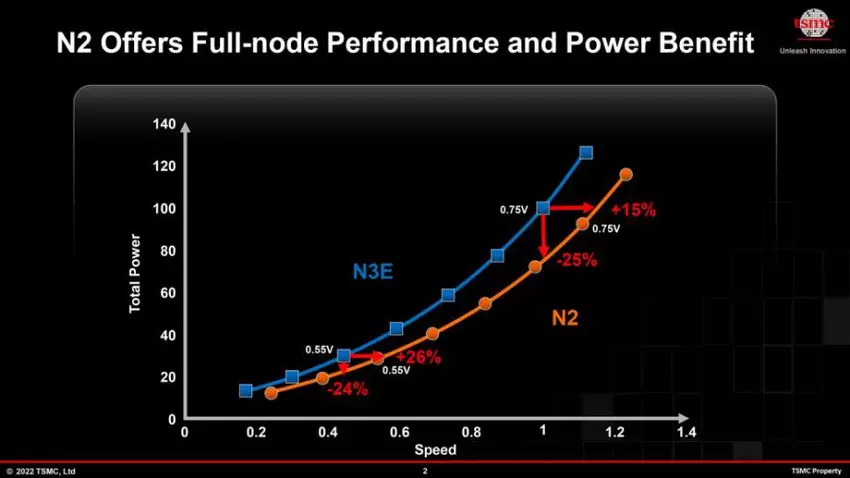

Przy tym samym poborze mocy węzeł 2 nm poprawia wydajność o 10% do 15%, jednocześnie zmniejszając zużycie energii o 25% do 30% w porównaniu z generacją N3E. Gęstość wiórów jest wyższa w przypadku N2 niż w przypadku N3E (1,1 razy).

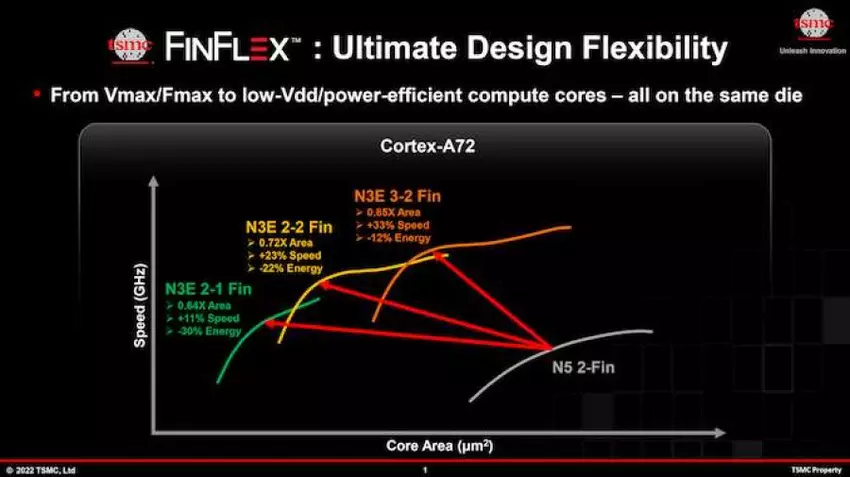

Ponadto TSMC wprowadziło GAAFET (tranzystory polowe typu „gate-all-around”). Nowe tranzystory z nanoarkuszami zwiększą wydajność na wat poprzez zmniejszenie rezystancji.

W tym samym czasie Samsung Foundry rozpocznie masową produkcję chipów 3 nm w 2022 roku, a amd planuje rozpocząć produkcję chipów 2 nm również w 2025 roku.